Scale-Up大战开打:各厂技术路线、中国厂商发展与产业价值链解析

摘要

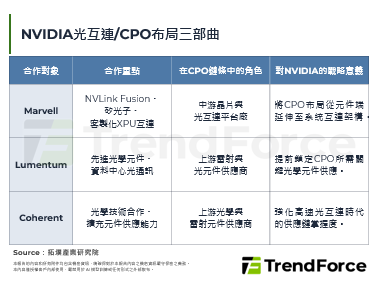

近期NVIDIA宣布推出可供客户在自有ASIC使用NVLink的NVLink Fusion,以及与Intel合作x86 CPU,大幅增加NVLink使用情境,又针对Inference的Prefill阶段推出Rubin CPX/VR200 NVL144 CPX新机架概念,在Rubin CPX晶片间改采用PCIe 6互连。此外,UALink、SUE等开放标准也逐渐酝酿成形。中国华为近期宣布2026年第四季的Atlas 950 SuperPOD将采用UB 2.0技术,并对外开放。

在AI运算需求大幅提升下,将多个XPU高速串连成大型SuperPOD的Scale-Up技术俨然已成为算力提升关键,而Scale-Up市场也出现百家争鸣局面。本篇报告主要深度解析:(1) Scale-Up技术背景;(2) NVIDIA的Scale-Up版图与同业竞争情形;(3)中国Scale-Up发展;(4) Scale-Up Switch IC需求估计。期能提供厂商进行市场选择、价值评估的策略建议。

一. 背景概述

二. Scale-Up技术背景

三. Scale-Up竞争格局

四. 中国Scale-Up发展

五. Switch IC需求量估算

六. 拓墣观点

图一 3种扩展定律(Scaling Law)

图二 AI Model Training compute(FLOP)

图三 2021~2025年主要CSP季资本支出

图四 Scale-Up、Scale-Out、Scale-Across示意图

图五 传统单端讯号示意图

图六 GRS运作示意图

图七 Clos Topology

图八 Torus Topology

图九 Full-Mesh Topology

图十 Dragonfly Topology

图十一 Dragonfly+Topology

图十二 NVLink 1.0~4.0网路架构

图十三 主要调变技术

图十四 NVLink 5.0网路架构

图十五 NVIDIA技术Roadmap

图十六 VR300 NVL576

图十七 NVLink Fusion示意图

图十八 RTX Pro Server

图十九 Rubin CPX

图二十 UALink 1.0架构

图二十一 MI400 Helios rack

图二十二 SUE架构

图二十三 UB-Mesh互连架构

图二十四 CloudMatrix384 Level 1互连架构

图二十五 CloudMatrix384 Level 2互连架构

图二十六 ALS架构

图二十七 ETH-X架构

表一 Scale-Up、Scale-Out、Scale-Across比较

表二 主要网路拓朴类别

表三 主要网路拓朴的优缺点比较

表四 目前主要Scale-Up技术比较

表五 2014~2027年NVLink技术演进

表六 2024~2026年NVIDIA Rack Level网路硬体配置演进

表七 中国AI供应链

表八 中国主要AI加速器比较

表九 NVLink与中国Scale-Up技术比较

表十 各大厂商SuperPOD中Switch IC/XPU比例估计

表十一 2026年各大厂商Switch IC需求估计